library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

ENTITY NAND_GATE IS

PORT(A,B:IN STD_LOGIC;C:OUT STD_LOGIC);

END NAND_GATE;

ARCHITECTURE NAND_ARCH OF NAND_GATE IS

BEGIN

C<=(NOT(A AND B));

END NAND_ARCH;

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY HALF_ADDER IS

PORT(A,B:IN STD_LOGIC;SUM,CARRY:OUT STD_LOGIC);

END HALF_ADDER;

ARCHITECTURE HALF_ADDER_ARCH OF HALF_ADDER IS

SIGNAL X1,X2,X3:STD_LOGIC;

COMPONENT NAND_GATE

PORT(A,B:IN STD_LOGIC;C:OUT STD_LOGIC);

END COMPONENT;

BEGIN

STEP1:NAND_GATE PORT MAP (A,B,X1);

STEP2:NAND_GATE PORT MAP (A,X1,X2);

STEP3:NAND_GATE PORT MAP (B,X1,X3);

STEP4:NAND_GATE PORT MAP (X2,X3,SUM);

CARRY<=((A NAND B)NAND (A NAND B));

END HALF_ADDER_ARCH;

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY BITFULLADDER IS

PORT(A,B,CIN:IN STD_LOGIC;SUM,CARRY:OUT STD_LOGIC);

END BITFULLADDER;

ARCHITECTURE BITFULLADDER_ARCH OF BITFULLADDER IS

COMPONENT HALF_ADDER

PORT(A,B:IN STD_LOGIC;SUM,CARRY:OUT STD_LOGIC);

END COMPONENT;

SIGNAL Z1,C1,C2: STD_LOGIC;

BEGIN

STEP5:HALF_ADDER PORT MAP(A,B,Z1,C1);

STEP6:HALF_ADDER PORT MAP(CIN,Z1,SUM,C2);

CARRY<=((C1 NAND C1) NAND (C2 NAND C2));

END BITFULLADDER_ARCH;

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

use IEEE.numeric_bit.all;

entity multiplierr is

Port ( x : in STD_LOGIC_VECTOR (03 downto 0);

y : in STD_LOGIC_VECTOR (03 downto 0);

z : out STD_LOGIC_VECTOR (07 downto 0);

carry:out std_logic);

end multiplierr;

architecture Behavioral of multiplierr is

component BITFULLADDER

PORT(A,B,CIN:IN STD_LOGIC;SUM,CARRY:OUT STD_LOGIC);

END component;

signal a,b,c,d,j,k:std_logic_vector(7 downto 0 );

signal c0,c1,c2,c3,c4,c5,c6,c7,c00,c01,c02,c03,c04,c05,c06,c07,c000,c001,c002,c003,c004,c005,c006,c007:std_logic;

begin

process(x,y,a,b,c,d,j,k,c0,c1,c2,c3,c4,c5,c6,c7,c00,c01,c02,c03,c04,c05,c06,c07,c000,c001,c002,c003,c004,c005,c006,c007)

begin

if x(0)='1'

then a<='0000'&y;

else a<='0000'&'0000';

end if;

if x(1)='1'

then b<='000'&y&'0';

else b<='000'&'0000'&'0';

end if;

if x(2)='1'

then c<='00'&y&'00';

else c<='00'&'0000'&'00';

end if;

if x(3)='1'

then d<='0'&y&'000';

else d<='0'&'0000'&'000';

end if;

end process;

j0:BITFULLADDER port map (a(0),b(0),'0',j(0),c0);

j1:BITFULLADDER port map (a(1),b(1),c0,j(1),c1);

j2:BITFULLADDER port map (a(2),b(2),c1,j(2),c2);

j3:BITFULLADDER port map (a(3),b(3),c2,j(3),c3);

j4:BITFULLADDER port map (a(4),b(4),c3,j(4),c4);

j5:BITFULLADDER port map (a(5),b(5),c4,j(5),c5);

j6:BITFULLADDER port map (a(6),b(6),c5,j(6),c6);

j7:BITFULLADDER port map (a(7),b(7),c6,j(7),c7);

k0:BITFULLADDER port map (c(0),d(0),'0',k(0),c00);

k1:BITFULLADDER port map (c(1),d(1),c00,k(1),c01);

k2:BITFULLADDER port map (c(2),d(2),c01,k(2),c02);

k3:BITFULLADDER port map (c(3),d(3),c02,k(3),c03);

k4:BITFULLADDER port map (c(4),d(4),c03,k(4),c04);

k5:BITFULLADDER port map (c(5),d(5),c04,k(5),c05);

k6:BITFULLADDER port map (c(6),d(6),c05,k(6),c06);

k7:BITFULLADDER port map (c(7),d(7),c06,k(7),c07);

z0:BITFULLADDER port map (j(0),k(0),'0',z(0),c000);

z1:BITFULLADDER port map (j(1),k(1),c000,z(1),c001);

z2:BITFULLADDER port map (j(2),k(2),c001,z(2),c002);

z3:BITFULLADDER port map (j(3),k(3),c002,z(3),c003);

z4:BITFULLADDER port map (j(4),k(4),c003,z(4),c004);

z5:BITFULLADDER port map (j(5),k(5),c004,z(5),c005);

z6:BITFULLADDER port map (j(6),k(6),c005,z(6),c006);

z7:BITFULLADDER port map (j(7),k(7),c006,z(7),c007);

carry<= c7 xor c07 xor c007;

end Behavioral;

use IEEE.STD_LOGIC_1164.ALL;

ENTITY NAND_GATE IS

PORT(A,B:IN STD_LOGIC;C:OUT STD_LOGIC);

END NAND_GATE;

ARCHITECTURE NAND_ARCH OF NAND_GATE IS

BEGIN

C<=(NOT(A AND B));

END NAND_ARCH;

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY HALF_ADDER IS

PORT(A,B:IN STD_LOGIC;SUM,CARRY:OUT STD_LOGIC);

END HALF_ADDER;

ARCHITECTURE HALF_ADDER_ARCH OF HALF_ADDER IS

SIGNAL X1,X2,X3:STD_LOGIC;

COMPONENT NAND_GATE

PORT(A,B:IN STD_LOGIC;C:OUT STD_LOGIC);

END COMPONENT;

BEGIN

STEP1:NAND_GATE PORT MAP (A,B,X1);

STEP2:NAND_GATE PORT MAP (A,X1,X2);

STEP3:NAND_GATE PORT MAP (B,X1,X3);

STEP4:NAND_GATE PORT MAP (X2,X3,SUM);

CARRY<=((A NAND B)NAND (A NAND B));

END HALF_ADDER_ARCH;

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY BITFULLADDER IS

PORT(A,B,CIN:IN STD_LOGIC;SUM,CARRY:OUT STD_LOGIC);

END BITFULLADDER;

ARCHITECTURE BITFULLADDER_ARCH OF BITFULLADDER IS

COMPONENT HALF_ADDER

PORT(A,B:IN STD_LOGIC;SUM,CARRY:OUT STD_LOGIC);

END COMPONENT;

SIGNAL Z1,C1,C2: STD_LOGIC;

BEGIN

STEP5:HALF_ADDER PORT MAP(A,B,Z1,C1);

STEP6:HALF_ADDER PORT MAP(CIN,Z1,SUM,C2);

CARRY<=((C1 NAND C1) NAND (C2 NAND C2));

END BITFULLADDER_ARCH;

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

use IEEE.numeric_bit.all;

entity multiplierr is

Port ( x : in STD_LOGIC_VECTOR (03 downto 0);

y : in STD_LOGIC_VECTOR (03 downto 0);

z : out STD_LOGIC_VECTOR (07 downto 0);

carry:out std_logic);

end multiplierr;

architecture Behavioral of multiplierr is

component BITFULLADDER

PORT(A,B,CIN:IN STD_LOGIC;SUM,CARRY:OUT STD_LOGIC);

END component;

signal a,b,c,d,j,k:std_logic_vector(7 downto 0 );

signal c0,c1,c2,c3,c4,c5,c6,c7,c00,c01,c02,c03,c04,c05,c06,c07,c000,c001,c002,c003,c004,c005,c006,c007:std_logic;

begin

process(x,y,a,b,c,d,j,k,c0,c1,c2,c3,c4,c5,c6,c7,c00,c01,c02,c03,c04,c05,c06,c07,c000,c001,c002,c003,c004,c005,c006,c007)

begin

if x(0)='1'

then a<='0000'&y;

else a<='0000'&'0000';

end if;

if x(1)='1'

then b<='000'&y&'0';

else b<='000'&'0000'&'0';

end if;

if x(2)='1'

then c<='00'&y&'00';

else c<='00'&'0000'&'00';

end if;

if x(3)='1'

then d<='0'&y&'000';

else d<='0'&'0000'&'000';

end if;

end process;

j0:BITFULLADDER port map (a(0),b(0),'0',j(0),c0);

j1:BITFULLADDER port map (a(1),b(1),c0,j(1),c1);

j2:BITFULLADDER port map (a(2),b(2),c1,j(2),c2);

j3:BITFULLADDER port map (a(3),b(3),c2,j(3),c3);

j4:BITFULLADDER port map (a(4),b(4),c3,j(4),c4);

j5:BITFULLADDER port map (a(5),b(5),c4,j(5),c5);

j6:BITFULLADDER port map (a(6),b(6),c5,j(6),c6);

j7:BITFULLADDER port map (a(7),b(7),c6,j(7),c7);

k0:BITFULLADDER port map (c(0),d(0),'0',k(0),c00);

k1:BITFULLADDER port map (c(1),d(1),c00,k(1),c01);

k2:BITFULLADDER port map (c(2),d(2),c01,k(2),c02);

k3:BITFULLADDER port map (c(3),d(3),c02,k(3),c03);

k4:BITFULLADDER port map (c(4),d(4),c03,k(4),c04);

k5:BITFULLADDER port map (c(5),d(5),c04,k(5),c05);

k6:BITFULLADDER port map (c(6),d(6),c05,k(6),c06);

k7:BITFULLADDER port map (c(7),d(7),c06,k(7),c07);

z0:BITFULLADDER port map (j(0),k(0),'0',z(0),c000);

z1:BITFULLADDER port map (j(1),k(1),c000,z(1),c001);

z2:BITFULLADDER port map (j(2),k(2),c001,z(2),c002);

z3:BITFULLADDER port map (j(3),k(3),c002,z(3),c003);

z4:BITFULLADDER port map (j(4),k(4),c003,z(4),c004);

z5:BITFULLADDER port map (j(5),k(5),c004,z(5),c005);

z6:BITFULLADDER port map (j(6),k(6),c005,z(6),c006);

z7:BITFULLADDER port map (j(7),k(7),c006,z(7),c007);

carry<= c7 xor c07 xor c007;

end Behavioral;

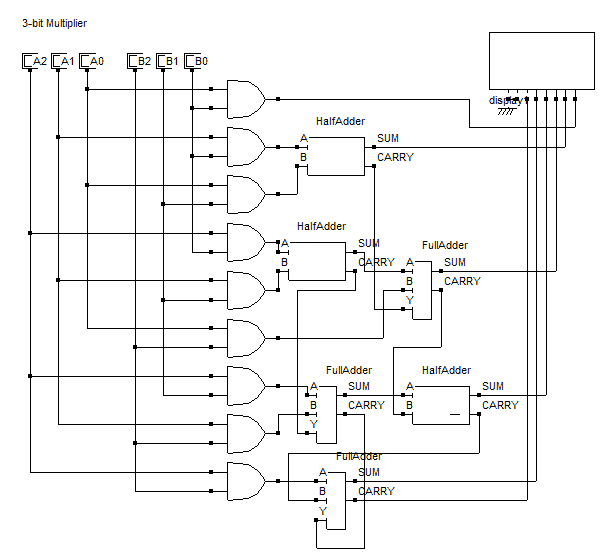

4 Bit Multiplier Vhdl

32 Bit Multiplier Vhdl

Mar 20, 2018 The VHDL source code for a parallel multiplier, using 'generate' to make the VHDL source code small is mul32c.vhdl The test bench is mul32ctest.vhdl The output of the simulation is. VHDL Code Examples for Flip Flop, Serial to Parallel Converter, 4 bit Counter, State Machine, and ADDER. Mar 28, 2020 In this article, we will be writing the VHDL code for a 2-bit binary multiplier using all the three modeling techniques. We will write the code, testbench and will also create the RTL schematics for the same.